22/08/22 FLÁVIO BRAGANÇA EXPLICADORES.NET

## **INSTRUÇÕES**

- COMANDOS INTERNOS DO PROCESSADOR;

- TODO PROCESSADOR TEM UM CONJUNTO FINITO DE INSTRUÇÕES;

- A CADA NOVO LANÇAMENTO DE PROCESSADOR NOVAS INSTRUÇÕES VÃO SENDO ACRESCENTADAS;

# TIPOS DE INSTRUÇÕES

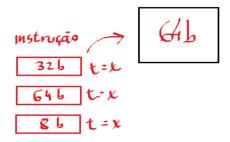

### **SISD**

SINGLE INSTRUCTION SINGLE DATA;

- CADA INSTRUÇÃO CARREGA SOMENTE UMA INFORMAÇÃO;

- UMA INSTRUÇÃO SEMPRE CARREGA OS DADOS DELA MESMA;

- UMA INSTRUÇÃO NÃO É CAPAZ DE JUNTAR A OUTRA PARA OTIMIZAR A VELOCIDADE;

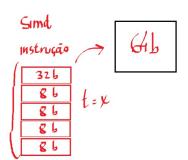

### **SIMD**

SINGLE INSTRUCTION MULTIPLE DATA;

- CADA INSTRUÇÃO CARREGA MÚLTIPLAS INFORMAÇÕES;

- CADA INSTRUÇÃO PODE SE JUNTAR A OUTRAS PARA OTIMIZAR O PROCESSAMENTO;

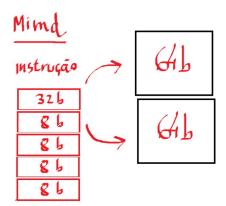

#### **MIMD**

MULTIPLE INSTRUCTION MULTIPLE DATA;

- VÁRIAS INSTRUÇÕES CARREGAM VÁRIAS INFORMAÇÕES;

- MULTICORE (PROCESSADOR COM VÁRIOS NÚCLEOS);

- QUANDO VÁRIAS INSTRUÇÕES UNIDAS (SIMD) SÃO EXECUTADAS POR PROCESSADORES DE VÁRIOS NÚCLEOS:

## TIPOS TIPO SIMD/MIMD (GRAU DE PARALELISMO DAS INSTRUÇÕES)

### **MMX**

- 57 NOVAS INSTUÇÕES SIMD DA INTEL;

### 3DNOW!

- SIMD DA AMD;

### **SSE**

- STREAMMING SIMD EXTENSIONS;

- FACILITAM O STREAMMING;

### SSE<sub>2</sub>

- STREAMMING SIMD EXTENSIONS 2;

- FACILITAM O STREAMMING;

### SSE3

- STREAMMING SIMD EXTENSIONS 3;

- FACILITAM O STREAMMING;

# SSE4

- STREAMMING SIMD EXTENSIONS 4;

- FACILITAM O STREAMMING;

### **AES-NI**

- ADVANCED ENCRIPYTION STANDARD NEW INSTRUCTIONS;

- CRIPTOGRAFIA WI-FI;

### **MEMÓRIA CACHE**

### **FUNCÃO:**

- ACELERAR PROCESSAMENTOS REPETIDOS;

- 70 % MAIS RÁPIDA QUE A RAM;

- MENOR QUE A RAM;

- INTERPOSTA ENTRE O PROCESSADOR E RAM;

- ESTÁ MAIS PRÓXIMA DO PROCESSADOR QUE A RAM;

- VOLÁTIL (QUANDO CORTAMOS A ENERGIA OS DADOS SÃO PERDIDOS;

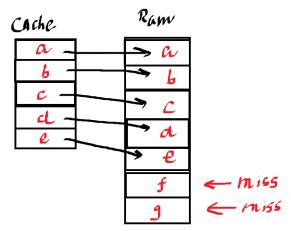

- TRABALHA COM SOBREPOSIÇÃO;

- CACHE HIT SINAL GERADO QUANDO O PROGRAMA É EXECUTADO NA CACHE;

- CACHE MISS SINAL GERADO QUANDO O PROGRAMA NÃO É EXECUTADO NA CACHE E SIM NA RAM;

## **CLASSIFICAÇÕES DA CACHE:**

# QUANTO AO POSICIONAMENTO NO SISTEMA

L1 - LEVEL 1 – NÍVEL 1 (MAIS PRÓXIMA DO PROCESSADOR) (MAIOR VELOCIDADE)

L2 - LEVEL 2 - NÍVEL 2

L3 - LEVEL 3 - NÍVEL 3

L4 - LEVEL 4 - NÍVEL 4

L5 - LEVEL 5 – NÍVEL 5 (MAIS DISTANTE DO PROCESSADOR) (MENOR VELOCIDADE)

## QUANTO AOS ESQUEMAS DE ATUALIZAÇÃO DE CACHE

Quando a cache atualiza a Ram com os dados que foram alterados

#### WRITE THROUGH

- Quando algo muda na cache imediatamente é alterado na RAM;

- A Ram nunca fica desatualizada;

- Aumenta a probabilidade de cache Hit;

- Mais trabalhoso para o sistema;

- Parte da cache:

### WRITE BACK

- Quando algo é modificado na cache só será atualizado na Ram quando a mesma solicitar;

- A Ram pode ficar desatulizada;

- Diminui a probabilidade de cache hit;

- Menos trabalho para o sistema;

- Parte da RAM;

# QUANTO A ARQUITETURA DE CONSTRUÇÃO

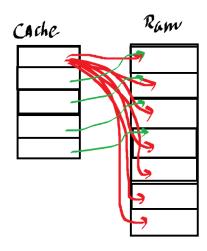

### CACHE COM MAPEAMENTO DIRETO

- OS MÓDULOS DE CACHE SÃO DIRETAMENTE CONECTADOS DE MANEIRA FIXA COM OS MÓDULOS DE RAM;

- OS MÓDULOS QUE NÃO SÃO MAPEADOS NUNCA ENTRAM EM CACHE;

- REDUZ A QUANTIDADE DE CACHE HIT;

- MAIS SIMPLES PARA O SISTEMA;

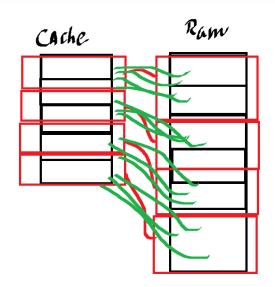

### **CACHE COMPLETAMENTE ASSOCIATIVO**

- QUALQUER MÓDULO DE CACHE PODE MAPEAR QUALQUER MÓDULO DE RAM;

- AUMENTA QUANTIDADE DE CACHE HIT;

- MAIS COMPLEXO PARA O SISTEMA;

### CACHE ASSOCIATIVO POR CONJUNTOS/GRUPOS

- DIVIDE A CACHE EM QUATRO CACHES COMPLETAMENTE ASSOCIATIVAS;

- CADA GRUPO SE CONECTA A UM GRUPO DE RAM;

- DIMINUI A COMPLEXIDADE

- AUMENTA O CACHE HIT

- MAIS UTILIZADO ATUALMENTE;

- UNE O MELHOR DAS ARQUITETURA ANTERIORES;

### TECNOLOGIAS DE AUMENTO DE DESEMPENHO

### PREVISÃO DE DESVIO

- PREVISÃO DOS DESVIOS CONDICIONAIS;

- Tecnologia que tenta adivinhar o que o processador poderá executar. Esta tecnologia se resume em carregar na memória todos os desvios condicionais possíveis (se, case etc), e deixá-los prontos na memória para quando forem requistados.

### **PIPELINE**

- LINHA DE PRODUÇÃO;

- QUANDO AS INSTRUÇÃO PASSAM ETAPA A ETAPA;

- NÃO DEIXA AS UNIDADES OCIOSAS:

| PRÉ-BUSCA       | – PRÉ FETCH                    | - | INST06 |

|-----------------|--------------------------------|---|--------|

| BUSCA           | – FETCH                        | - | INST05 |

| DECODIFICAÇÃO   | <ul><li>DECODE</li></ul>       | - | INST04 |

| BUSCA DOS DADOS | <ul> <li>DATA FETCH</li> </ul> | - | INST03 |

| EXECUÇÃO        | <ul><li>EXECUTION</li></ul>    | - | INST02 |

| RESPOSTA        | <ul><li>WRITE BACK</li></ul>   | - | INST01 |

### **SUPERESCALAR**

- PROCESSADOR COM MAIS DE UM PIPELINE;

- PELO MENOS DUAS:

- SUPERESCALAR DE DUPLA CANALIZAÇÃO (2);

- SUPERESCALAR DE TRIPLA CANALIZAÇÃO (3);

PF F D DF E WB

### EXECUÇÃO FORA DE ORDEM

- OTIMIZAÇÃO DA FILA OU DA PILHA DE INSTRUÇÕES;

- QUANDO O PROCESSADOR DEIXA PASSAR NA FRENTE INSTRUÇÕES QUE SERIAM EXECUTADAS MAIS RAPIDAMENTE;

- TROCAR A ORDEM DA PRIORIDADE DAS INSTRUÇÕES VISANDO OTIMIZAR A FILA;

## EXECUÇÃO ESPECULATIVA

- MELHORIA DA PREVISÃO DE DESVIO;

- ALGUMAS INSTRUÇÕES GENÉRICAS FICAM PRONTAS;

- ESPERANDO QUE SEJAM EXECUTADAS EM ALGUM MOMENTO;

#### RENOMEAMENTO DE REGISTRADORES

TROCAR A FUNÇÃO DE REGISTRADORES QUE ESTÃO OCIOSOS PARA ATENDER A UMA NECESSIDADE IMEDIATA;

### ARQUITETURA HÍBRIDA RISC/CISC

O PROCESSADOR É CAPAZ DE COMPREENDER OS DOIS TIPOS DE INSTRUÇÃO;

### **FUSÃO DE INSTRUCÕES**

QUANDO O PROCESSADOR UNE VÁRIAS INSTRUÇÕES EM UMA, OTIMIZANDO O TEMPO DE PROCESSAMENTO (EX.: SIMD);

### TECNOLOGIAS DE MÚLTIPLOS NÚCLEOS

- QUANDO VÁRIOS PROCESSADORES SÃO COLOCADOS EM UM ÚNICO INVÓLUCRO;

- FUNCIONA COMO MULTIPROCESSADORES;

- DUAL CORE DOIS NÚCLEOS;

- QUAD CORES QUATRO NÚCLEOS;

- OCTA CORE OITO NÚCLES;

### **HYPER THREADING (HT)**

- PEGA AS PARTES OCIOSAS DO PROCESSADOR E GERA NÚCLEOS VIRTUAIS;

- AUMENTANDO A QUANTIDADE DE NÚCLEOS;

### **OVERCLOCK DINÂMICO**

- Aumentar o clock somente quando necessário;

- Reduz em programas que exigem menos processamento (reduz o consumo de energia);

- Aumenta quando usamos um programa que exige mais processamento (Aumenta o consumo de energia);

OBS.:

### **OVERCLOCK**

- Ato de configurar o processador com um clock acima do especificado;

- Durabilidade reduzida;

- Aquece mais;

- Processador / RAM / GPU;

$1.7Ghz \rightarrow 2Ghz$

### **UNDERCLOCK**

- Ato de configurar o processador com um clock **aquém** do especificado;