EXPLICADORES.NET 19/12/22 FLÁVIO BRAGANÇA HARDWARE

### Organização da memória

#### Introdução

Na arquitetura X86, por motivos históricos, considera-se que cada endereço de memória armazena dados de oito bits, e é por isso que continuamos nos referindo á capacidade de memória em **BYTES**;

### 160 MiB (160 Mibi Bytes)

### Representação de endereços

Há duas formas de se representar endereços.

**Endereçamento linear/PLANO** – Endereços numerados sequencialmente, funcioanando no modo protegido e no modo de 64 bits.

- CRESCENTE;

- O PRIMEIRO ENDEREÇO É O MENOR;

- O ÚLTIMO ENDEREÇO É O MAIOR;

- O ENDEREÇO É FORMADO APENAS POR UM NÚMERO;

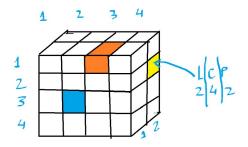

**Endereçamento segmentado** – Neste sistema, os endereços são representados no formato segmento:offset. Um seguimento é um pedaço da memória do computador, enquanto que o offset (deslocamento) é a posição do dado a ser lido ou armazenado dentro desse bloco de memória.

- OFFSET = PROFUNDIDADE;

- LINHA, COLUNA E PROFUNDIDADE;

TODOS OS ENDEREÇOS DE MEMÓRIA ESTÃO NA BASE (16) → HEXADECIMAL

# Organização da memória no modo real

#### **SEGMENTADO**

No modo real a memória é dividida em segmentos de 64KiB. No modo de endereçamento segmentado.

#### Organização da memória no modo protegido

No modo protegido a memória pode ser acessada de uma das seguintes maneiras por programas:

**Modo Plano/LINEAR básico :** Neste modo, a memória é acessada como uma entidade única, sem qualquer tipo de segmentação.

**Modo plano/LINEAR protegido :** Igual ao anterior, porém o processador é configurado para que uma exceção (mensagem de erro) seja dada caso o processador tente acessar uma área de memória acima da que está fisicamente instalada no computador.

**Modo multisSEGEMENTADO**: É o modelo normalmente usado quando estamos trabalhando no modo protegido. Neste modo a memória é dividida em segmentos de tamanho variado, e estes segmentos podem ser protegidos, ou amarrados a um programa específico. Fazendo que um programa não invada a área de memória que está sendo utilizada por outro.

MODO

MODO REAL MODO PROTEGIDO TIPO DE ENDEREÇAMENTO SEGMENTADO PLANO OU SEGMENTADO

#### Proteção de memória

#### Introdução

- → IMPEDE QUE UM PROGRAMA INVADA A ÁREA DO OUTRO;

- → PROTEGE UM PROGRAMA DE INVADIR A ÁREA DE OUTRO PROGRAMA;

- → A PROTEÇÃO DE MEMÓRIA ESTÁ NO HARDWARE;

- ightarrow GPF ightarrow GENERAL PROTECTION FAILURE ightarrow FALHA GERAL NA PROTEÇÃO, MESMO QUE O HARDWARE TENHA A PROTEÇÃO DE MEMÓRIA O SISTEMA OPERACIONAL PODE CAUSAR ESTE ERRO;

No modo protegido cada segmento é uma área protegida de memória, que só pode ser acessada por um programa específico. Com isso, para cada segmento de memória, o sistema operacional precisa saber:

#### ESTE RECURSO SÓ É APLICADO NO MODO PROTEGIDO:

**MODO REAL**  $\rightarrow$  POUCOS RECURSOS  $\rightarrow$  BAIXA PERFORMANCE  $\rightarrow$  COMPATIBILIDADE (PROGRAMAS ANTIGOS RODANDO EM UM SISTEMA NOVO;

**MODO PROTEGIDO** → MODO ONDE O PROCESSADOR ESTÁ NA SUA CAPACIDADE MÁXIMA DE PERFORMANCE;

#### Paginação

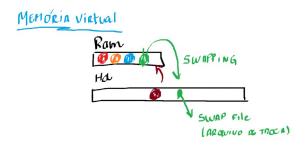

- SWAPPING  $\rightarrow$  PROCEDIMENTO DE TROCA DE INFORMAÇÕES ENTRE O HD E A RAM;

- SWAP FILE → ARQUIVO DE TROCA, ARQUIVO GERADO NO HD COM AS INFORMAÇÕES ORIUNDAS DA RAM;

- O HD É MUITO MAIS LENTO QUE A RAM;

- A MEMÓRIA VIRTUAL É UMA SOLUÇÃO PARA A FALTA DE MEMÓRIA;

- PORÉM O USO DO HD PREJUDICA À PERFORMANCE:

MEMÓRIA TOTAL = RAM +ESPAÇO DE SWAP

QUANDO USAMOS A MEMÓRIA RAM COM MEMÓRIA VIRTUAL, A MEMÓRIA SERÁ DIVIDIDA DE DUAS MANEIRAS:

- → PAGINAÇÃO;

- A MEMÓRIA É DIVIDA EM PÁGINAS, DE TAMANHO PADRONIZADO;

- TODAS AS PÁGINAS DE UMA MEMÓRIA TEM SEMPRE O MESMO TAMANHO;

- MEMÓRIAS DIFERETES PODEM TER PÁGINAS DE TAMANHO DIFERENTE:

|               |    |                      |     |       |        | ~  |    |

|---------------|----|----------------------|-----|-------|--------|----|----|

|               | SE | $\sim$ R $^{\prime}$ |     | 17    | $\sim$ |    | ١. |

| $\rightarrow$ | >- | ( ¬ IV               | חחו | 4 I A | 41.    | Δι | J. |

| ,             |    | <b>U</b> ::          |     | •     | ~ Y    |    | -, |

A MEMÓRIA É DIVIDIDA EM PEDAÇOS DE TAMANHO VARIADO; O TAMANHO DE CADA SEGMENTO DEPENDE DO SISTEMA OPERACIONAL:

O sistema de paginação permite o uso de memória virtual, permitindo que o processador acesse mais memória ram do que existe no computador quando ele está no modo protegido ou quando ele está no modo de 64 bits, simulando a memória faltosa em um disco de armazenamento em massa, como por exemplo o HD. Quando o sistema de memória virtual está desabilitado, cada endereço linear interno do processador corresponderá a um endereço físico externo da memória ram. Porém quando o sistema está habilitado, a memória ram é dividida em blocos chamados páginas. No disco um arquivo chamado arquivo de troca ou swap file é criado e dividido em blocos de igual tamanho.

#### Modos de paginação:

**Paginação de 32 bits :** Pode usar páginas e 4KiB ou de 4 MiB ( se o processador tiver a extensão PSE. Page Size Extensions.

Paginação PAE (Physical Address Extensions): Pode usar páginas de 4 KiB ou 2 MiB;

**Paginação IA-32e** (modo 64 bits): Pode usar páginas de 4 KiB, 2MiB ou 1GiB (nem todos os processadores suportam páginas de 1GiB);

O modo de paginação utilizado dependerá do sistema operacional.

#### Multitarefa

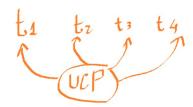

TIME SLICING→ TÉCNICA ONDE O PROCESSADOR FICA UMA FATIA DE TEMPO EM CADA TAREFA;

TIME SLICE → FATIA DE TEMPO, TEMPO QUE O PROCESSADOR FICA EM CADA TAREFA;

A multitarefa é um recurso que permite que o processador execute um pouco de cada programa que está carregando por vez, importante lembrar que neste tipo de contexto o sistema operacional também é um programa.

A técnica empregada é a técnica de time slicing (fatiando o tempo) onde cada programa será executado em uma fatia de tempo.

O controle da multitarefa pode ser feito por hardware ou por software.

O controle de multitarefa por hardware só existe no **modo protegido**.

O modo 64 bits faz o controle de multitarefa por software.

A **MULTITAREFA REAL** SÓ ACONTECE QUANDO TEMOS VÁRIOS PROCESSADORES:

→ VÁRIOS PROCESSADORES NA MESMA PLACA MÃE (MULTIPROCESSADORES):

→ VÁRIOS NÚCLEOS DENTRO DE UM ÚNICO PROCESSADOR;

#### Registradores

- MEMÓRIAS MAIS RÁPIDAS QUE EXISTEM;

- MENORES MEMÓRIAS QUE EXISTEM;

- MEMÓRIAS INTERNAS DO PROCESSADOR:

#### Registradores de uso geral

REGISTRADORES QUE PODEM SER USADOS PELOS PROGRAMADORES:

Registradores que podem ser usados livremente pelo programador. Também chamados de GPR (General Purpose Registrer ).

GPS = GLOBAL POSITION SYSTEM

GPF = GERERAL PROTECTION FAILURE GPR = GENERAL PURPOSE REGISTER

A arquitetura x86 possui 4 registradores e uso geral, são eles: (A,B,C,D)

**A (Acumulador):** Normalmente usado para armazenar dados a serem manipulados e resultados de operações.

#### NORMALMALMENTE UTILIZADO PARA GUARDAR RESULTADOS PARCIAIS;

**B** (Base): Normalmente usado para armazenar informações de endereçamento.

### ENDEREÇO ONDE A INFORMAÇÃO ESTÁ ARMAZENADA

**C** (**Contador**) : Normalmente usado como contador de lações (loops).

### **VARIÁVEL CONTADORA NOS LOOPS;**

**D** (**Dados**) : Normalmente usado para armazenar informações de entrada e saída.

#### **ARMAZENAM OS DADOS**

#### **Flags**

A arquitetura X86 possui um registrador de 32bits chamado de EFLAGS que armazena diversos FLAGS.

#### FLAGS → SITUAÇÕES QUE ACONTECEM NO SISTEMA

#### Registradores de controle

São utilizados para armazenar o **modo de operação do processador** e a caracteística da tarefa a sendo executada no momento.

Os principais tipos são :

CR1, CR2, CR3, CR4, CR5, CR6, CR7, CR8 e EFER.

- MODO REAL

- MODO PROTEGIDO

#### Registradores de Debug

DEBUG → COMPILAÇÃO PASSO A PASSO; EXECUTAR O PROGRAMA AOS POUCOS PARA DESVENDAR ERROS;

Os processadores X86 tem **suporte a Debugs** ( encontrar falhas e problemas em programas), estas informações ficam armazenadas em registradores de debug chamados de

DR0, DR1, DR2, DR3, DR4, DR5, DR6, DR7.

#### Registradores de gerenciamento do memória

Responsáveis pelo controle de operações na memória, são eles:

→ TODAS AS OPERÇÕES NECESSÁRIAS PARA A MEMÓRIA FUNCIONAR;

GDTR, LDTR, IDTR, TR;

#### Outros registradores

Cada processador poderá ter outros registradores específicos.

# REGISTRADORES ESPECÍFICOS PARA CADA FABRICANTE;

### Interrupções e exceções

#### Interrupções

São procedimentos executados pelo dispositivos que pedem a atenção do processador.

Exsitem três tipos de Interrupções:

$DISPOSITIVO \rightarrow INTERRUPÇÃO \rightarrow PROCESSADOR$

#### Interrupção de <u>hardware</u> mascarável

Interrupções de dispositivos.

#### PODE SER IGNORADA MOMENTANEAMENTE

### **PINO INTR**

O fato do processador possuir apenas uma linha para requisições de interrupções exige que exista um controlador de interrupções externo, que faz o papel de árbitro das isntruções que por ventura utilizarão este referido pino do processador. Utilizam o pino INTR.

#### Interrupções de <u>hardware</u> não mascarável

Interrupções de dispositivos.

NÃO PODE SER IGNORADA MOMENTANEAMENTE

PINO NMI (NO MASCARABLE INTERRUPTION)

Utilizam o pino NMI para pedidos de interrupções

## Interrupções de software

# INTERRUPÇÕES GERADAS POR PROGRAMAS

#### **PINO INT**

Utilizam o pino INT para pedidos de interrupções.

|  | _ |  |  |

|--|---|--|--|

|  |   |  |  |

INTERRUPÇÃO DE HARDWARE MASCARÁVEL INTERRUPÇÃO DE HARDWARE NÃO MASCARÁVEL INTERRUPÇÃO DE SOFTWARE INTERRUPÇÃO IPI PINO INTR NMI INT IPI

# **APIC (Advanced Programmable Interrupt Controller)**

Controlador interno do processador responsável por lidar com estas interrupções.

# INTERRUPÇÃO IPI

OBS.: Ainda existe um quarto tipo de interrupção chamada de IPI (Interprocessor Interruption), que é utilizada em sistemas **multiprocessados.**

#### **Exceções**

Outra maneira de fazer o processador parar a execução do programa atual é através da exceção de software. Funciona como uma mensagem de erro interna do processador.

Exceções possíveis dos processadores X86:

**Divisão por zero :** Uma instrução tentou executar uma divisão por zero; **Debug :** O contador de programa atingiu um dos endereços de parada.

Parada: O programa atingiu uma instrução de parada;

**Overflow :** Ocorre quando o resultado de uma expressão não cabe no registrador destino:

Valor fora dos limites: Quando o valor está fora dos limites permitidos;

**Opcode inválido**: Gerada quando o processador encontra um valor que foi dado a ele como se fosse uma instrução, mas não corresponde a nenhuma instrução no conjunto de instruções;

**Dispositivo não disponível :** Quando o processador recebe uma instrução multimedia e o mesmo não possui co-processador matemático;

**Falha dupla encontrada :** Quando o processador encontra uma falha ao tentar executar o código responsável por lidar com a exceção encontrada;

TSS inválido: A tabela TSS de uma tarefa é inválida;

Segmento não presente: Quando o segmento de um registrador é inválidoo;

Exceção de pilha: Ocorre quando a pilha estoura ou está vazia;

**Falha geral de proteção** : Quando um programa invade a área de outro programa GPF;

Falha de página: Quando uma tabela ou página não está presente;

**Exceção da unidade de ponto flutuante :** Quando a unidade de ponto flutuante do computador encontra um erro;

**Verificação de alinhamento :** Gerada quando o endereço de memória não está alinhado:

**Exceção SIMD :** Gerada quando uma instrução SIMD gerou um erro.